Chaper 4 - 存储器

定义:用来存放大量程序(指令段)和数据的计算机部件

基本要求:容量大,速度快,成本低。

三级存储体系结构:高速缓冲存储器 - 主存 - 外存。产生原因是 CPU 执行命令的速度远远快于读取的速度。

-

主存

CPU 能直接编程访问的存储器。存放 CPU 需要执行的程序和需要处理的事情。

要求:随机访问、工作速度快、具有一定的存储容量。

-

外存

用来存放需要联机保存(CPU 不可直接访问,放入主存才能使用)但暂不使用的大量程序和数据

要求:容量足够大(导致速度很慢)

-

高速缓存

存放最近使用的程序和数据。是主存数据的副本。

要求:速度足够快(导致容量很小)

虚拟存储:主存 + 部分外存。需要解决存储空间分配、程序调度、虚实地址转换等问题

存储介质

凡是明显具有并能保持两种稳定状态的物质和器件,并且能够方便地与电信号进行转换,就可以作为存储介质。

种类:磁芯存储器、半导体存储器、磁表面存储器、光盘存储器。

- 磁芯存储器:基本单位是微型磁环

- 半导体存储器:分为双极型(ECL | TTL,非常快但是功耗打集成度低)、MOS 型(SRAM|DRAM),基本单位是晶体管(双极型晶体管(三极管)、单击型晶体管(场效应管))。

- SRAM 依靠双稳态触发器的两个稳定状态保存信息

- DRAM 依靠电容上电荷存储信息。需要主动刷新,不稳定。读取也是破坏性的,所以读了需要重新写

- 磁表面存储器:利用磁层上不同方向的磁化区域表示信息。(磁卡、磁盘等)

- 光盘存储器:利用光盘的有无表示信息。

存取方式

RAM

翻译:random access memory

含义:

- 可按地址随机地访问任一存储单元

- 访问各存储单元所需的读/写时间相同,与地址无关

ROM

翻译:read only memory

固存:用户不能编程 PROM:用户可一次编程 EPROM:用户可多次编程(紫外线擦除) EEPROM:用户可多次编程(电擦除) Flash Memory

SAM

翻译:sequential access memory

顺序存取存储器的信息是按记录块组织、顺序存放的,访问时间与信息存放位置有关。磁带是采取顺序存取方式的存储器。

进行的操作:等待-读/写;速度指标:avg等待时间、数据传输率

DAM

direct access memory

访问时读/写部件先直接指向一个小区域,再在该区域内顺序查找。访问时间与数据位置有关。

进行的操作:定位(寻道)、等待、读/写;速度指标:avg定位时间,avg等待时间,数据传输速率

具体半导体存储器介绍

MOS 型的电路结构有 PMOS、NMOS、CMOS

SRAM

静态 MOS 存储单元

定义:若 T1 通 T2 断,存入 0;T1 断 T2 通,存入1。感觉有点诡异,难道说 $\overline{W}$ 写入的才是我要的数据吗。读者自行分辨……

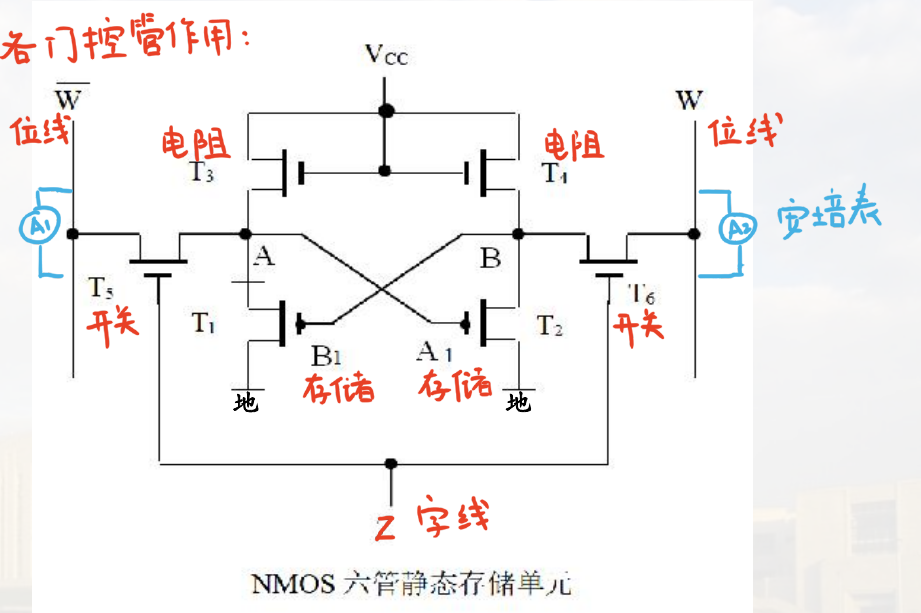

下图为 NMOS 的示意图:

图中单元介绍:

-

$V_{acc}$ 电源供电

-

$T_3,T_4$,电阻,分压

-

$T_1, T_2$,锁存专用的三极管

-

$T_5,T_6$,控制读写的开关

-

$W,\bar W$ 写入信号,位线,与之对应的 $Z$ 是字线

状态保持

当字线 $Z$ 为低电平(0)时,$T_5$ 和 $T_6$ 截止。

- 假设 A 点是 低电平 (0)。

- A点(0) $\to$ $T_2$ 的栅极 $\to$ $T_2$ 截止 $\to$ B点被 $T_4$ 拉高到 高电平 (1)。

- B点(1) $\to$ $T_1$ 的栅极 $\to$ $T_1$ 导通 $\to$ A点被强力拉低到地。

- 结果: 0 锁住了 1,1 反过来又锁住了 0。除非断电或强行改写,这个状态会永远保持。

读取操作

图中画了两个蓝色的安培表(A1, A2),这是为了演示读取时的电流差异。

- 预充电: 首先将两条位线 $\bar{W}$ 和 $W$ 都预充电到高电平。

- 选通: 字线 $Z$ 变高,$T_5, T_6$ 导通。

- 电流差异(关键逻辑):

- 假设内部存的是 A=0, B=1。

- 左侧: 位线 $\bar{W}$ 是高,A点是低。电流会从 $\bar{W}$ 流经 $T_5$,再经过导通的 $T_1$ 流向地。安培表 A1 会测到电流(或者位线电压下降)。

- 右侧: 位线 $W$ 是高,B点也是高。两边电位差不多,没有显著电流流向地($T_2$ 是截止的)。安培表 A2 测到的电流很小或为零。

- 结论: 外部电路通过检测哪边的电流大(或哪边电压掉得快),就知道里面存的是什么,所以是非破坏性读取。检测到 $\bar{W}$ 掉电,说明 A=0,存的数据是 0。

写入操作

写入依赖于驱动能力的覆盖。

- 假设里面存的是 A=0, B=1,我们要强行写入 0(即让 A=1, B=0)。

- 准备数据: 外部驱动电路强行将 $\bar{W}$ 置为高,$W$ 置为低 (0)。

- 选通: 字线 $Z$ 变高,$T_5, T_6$ 导通。

- 翻转逻辑(Overpowering):

- 重点看右边 B点。原本 B 被 $T_4$(电阻)拉高在 1。

- 现在,$W$ 线强行是 0,通过 $T_6$ 连到了 B。

- 设计关键: 开关管 $T_6$ 的导通能力(宽长比)必须设计得比负载管 $T_4$ 强得多。

- $T_6$ 会打败 $T_4$,强行把 B 点的电荷放掉,拉低到 0。

- 一旦 B 变成 0,$T_1$ 就截止了。

- $T_1$ 截止后,左边的 A 点就被 $T_3$ 和 $\bar{W}$(高)拉高到 1。

- 结果: 翻转完成,变为 A=1, B=0。

总结

- 字线 (Z) 决定了**“什么时候”**操作(控制开关 $T_5, T_6$)。

- 位线 (W, $\bar{W}$) 提供了**“数据通道”和“写入源”**。

- 负载 ($T_3, T_4$) 和 驱动 ($T_1, T_2$) 负责**“记住”**状态。它们利用正反馈,像跷跷板一样,一头高另一头必然低。

- 图中特别标注的电阻其实是指 $T_3/T_4$ 作为负载的高阻抗特性,这是为了保证 $T_1/T_2$ 导通时能把输出电压压得足够低,保证逻辑“0”的纯净度。

存储芯片

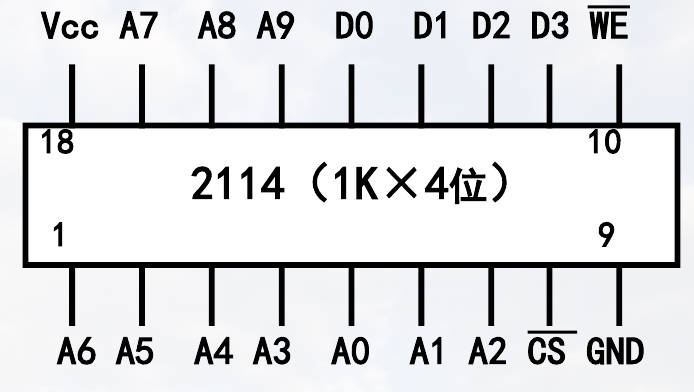

上图为 1k * 4 bit 的例子。

地址端:$A_9 \to A_0$ ($1k = 2^{10} = 0 \to 9$)

数据端:$D_3 \to D_0$

控制端:片选 $\overline{CS}$(0 选中该芯片,1 未选中),写使能端 $\overline{WE}$(0 写,1 读)。

电源 $V_{cc}$ ,接地端 $ GND$

DRAM

动态 MOS 存储单元

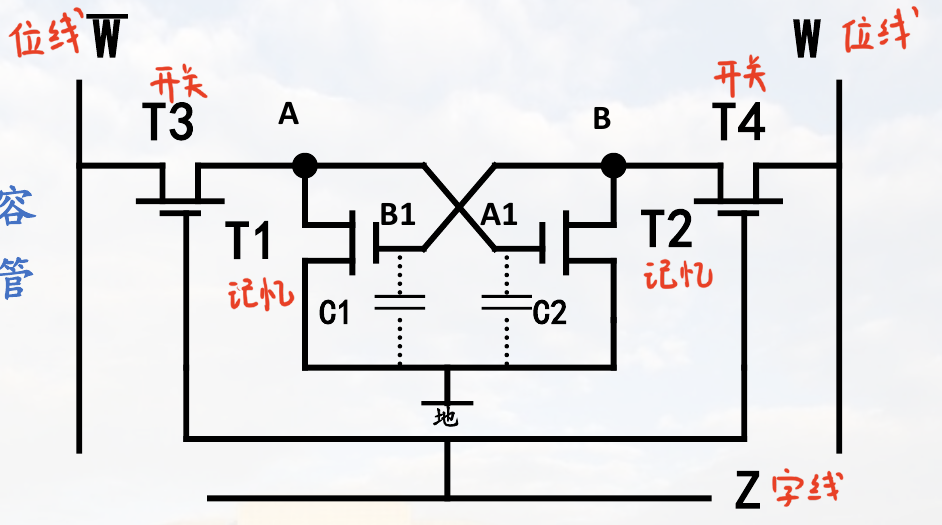

四管单元

通常定义电容 C2 充电至高电平为 1,低电平为 0。(显然两个电容动作相反)

$T_1$ 断开 $T_2$ 连通。

1)刷新:

在 MOS 管断开之后,电容内部总存在泄漏通路,难以使泄漏电阻达到无穷大。时间过长,电容上的电荷会通过泄漏电路放电,使所存储的信息丢失。为此,经过一定时间后就需要对存储内容重写一遍,也就是对存1的电容重新充电,称为刷新。

2)重写(再生):

对于单管动态 MOS 存储单元而言,读操作后电容C上的电荷将发生变化,属于破坏性读出,需要读后对存1的电容补充电荷,称为重写(再生)。这一过程,由芯片内的外围电路自动实现。

3)工作:

- 写入:先给 Z 加高电平,开启 $T_3, T_4$,再给 $\overline{W} $ 加高(1)/低(0)电平。后续分析以加低电平为例。若 $V_{A_1} < V_A$,则$V_{A_1} \downarrow~,C_2$ 上低下高,下方电荷流失,对地放电。同时 $T_2$ 由于 $V_{A_1}$ 为低电平而关闭。同时 W 加上与 $\overline{W}$ 相反的电平,同理分析可得,让 $T_1$ 执行与 $T_2$ 相反的动作。

- 读出:对 $\overline{W}$,$W$ 充电至略低于高电平的一个阈值量,然后对 Z 加高电平,打开 $ T_3, T_4 $。检测两条位线上的电流变化即知道读取的是 0 还是 1。e.g. $C_1$ 上有电荷时:$V_{B_1}$ 上为高电平,打开 $T_1$ ,$\overline{W} \to T_3 \to A \to T_1 \to ground$ 放电,$\overline{W}$上有电流通过,放大之后作为 0 读出。同时 $W \to T_4 \to B \to B_1 \to C_1$补充电荷。故四管不是破坏性读出,读出就是刷新。

- 保持:Z 加低电平,关闭放电回路,可以暂存几毫秒。

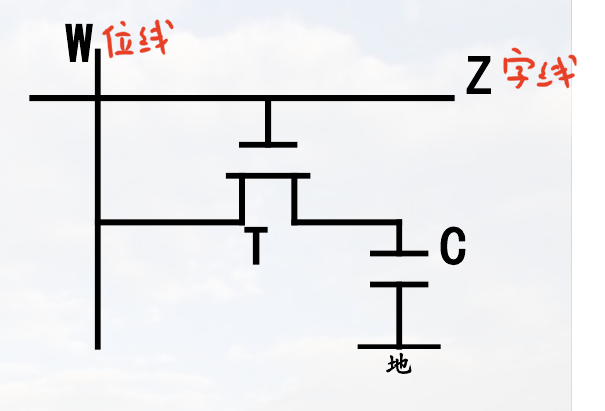

单管单元

- C:记忆单元

- T:控制门管

- Z:字线

- W:位线

定义:C 无电荷,电平低为 0。C 有电荷,电平高为 。

工作:

- 写入:字线加高电平,导通 T,位线上写 0/1。

- 读出:位线预充电到某一阈值,断开充电。字线加高电平,T 导通,根据 W 线电位的变化,读 1/0。

- 保持:Z 加低电平,T阶段。

注意是破坏性读出,读出后需要重新写入。

主存的设计

需要关注的问题:寻址逻辑(如何按地址选择芯片和片内单元),若采取 DRAM,考虑刷新问题。构成的主寸如何与 CPU 连接匹配,主存校验的问题。

总容量

字数×位数 = 总容量。(1 kB = 1k × 1B = $2^{10} \times 8 ~ bit$)

字数指可编址单元数,位数指每个单元的容量。大致于行号为可编址单元号,列号为每个单元的容量。

字数(编址空间)扩展

如果每一片的字数不够,用若干芯片组成总容量大的。(扩展行号)扩展的时候一般小容量芯片放地址低端,再安排大容量芯片,为了便于拟定片选逻辑。

位扩展

将芯片的数据输入输出线拼接。编址空间相同的芯片地址线和片选信号一样,故并联后与地址总线相接。

高位(或较高位)地址译码产生若干不同片选信号选择芯片,然后低位地址就直接送往芯片选择组内片内的某个编址单元。

存储器的设计

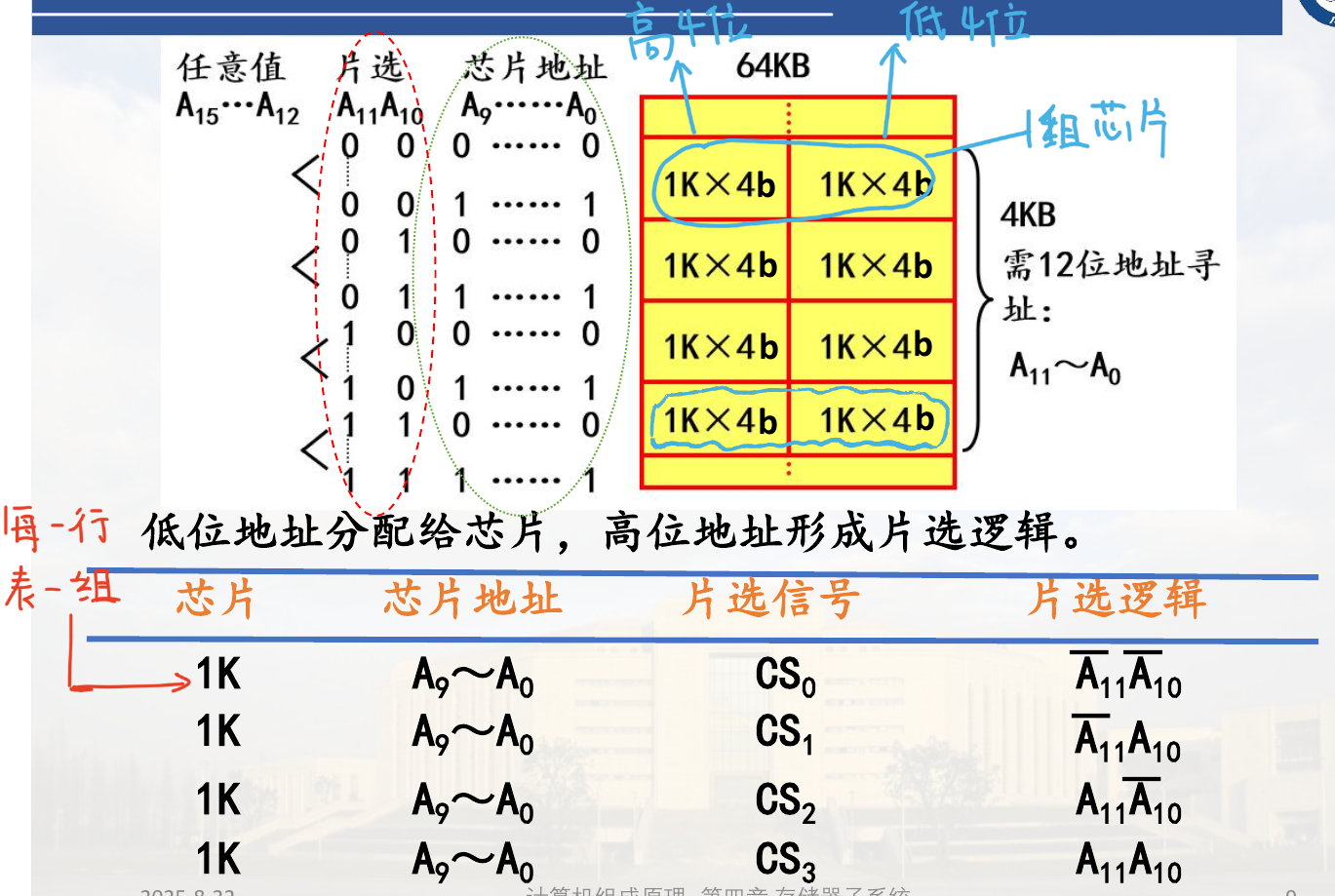

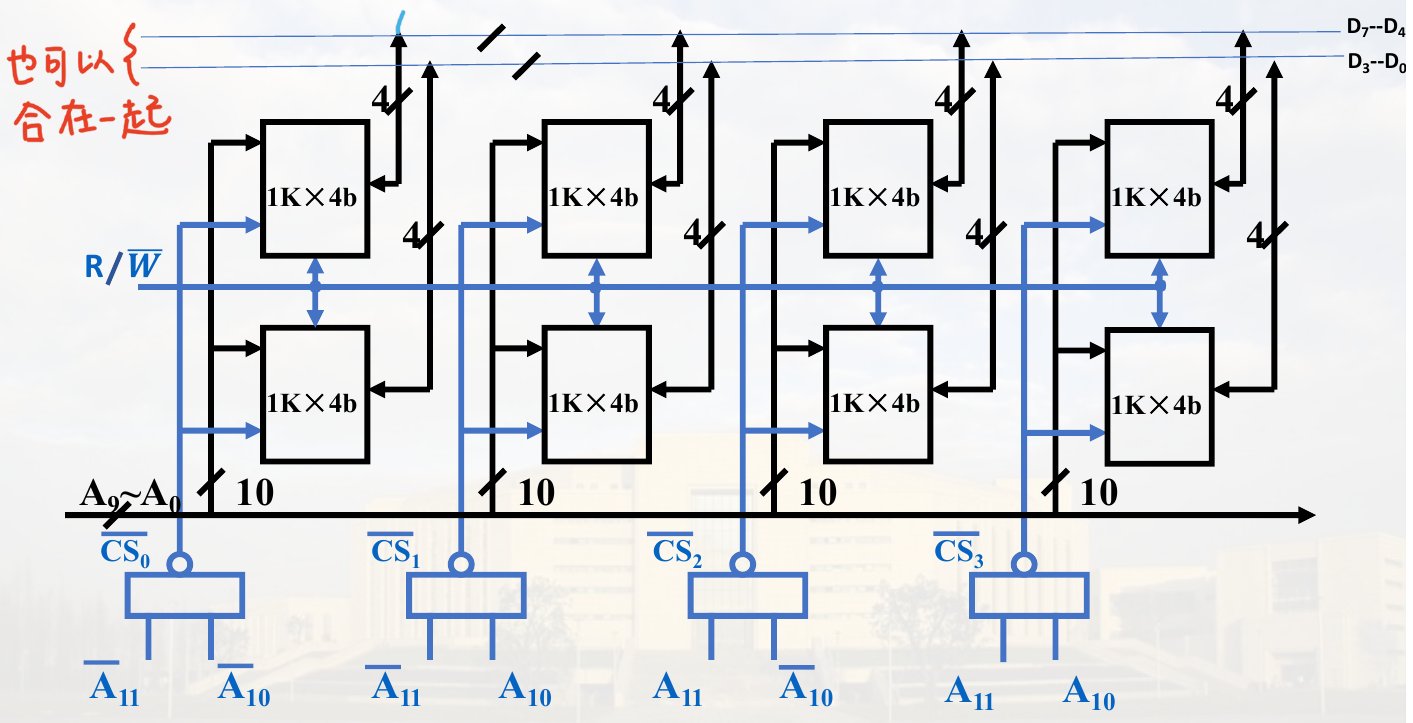

用 1k 4b 的芯片组成 4k 8b 的存储器。

首先计算芯片的数量。 每 1k 要用 2 块,有 4k,故 8 片。

然后考虑分配相关的逻辑。芯片外该如何进行地址分配(为芯片分配几位地址,便于寻找编址单元(行号))和片选(便于寻找芯片)。

这里都是 1k,所以分配 10 位($2^{10} = 1k$)即可,一般从低地址开始,即 ($A_9 \sim A_0$)。然后找芯片。一共 8 片,一行 2 片故一共只有 4 行。所以用 2 位($2^2 = 4$)表示芯片是哪一个即可,即($A_{11} \sim A_{10}$)片选信号从 0 开始编号,$CS_i$ 类似。芯片对应的片选逻辑是当前芯片选择位进行对应操作之后全 1 的。

例如图中低地址 00 就是两个取反。最后可以画出如下的图:

这个图中明确展现了片选信号如何产生的,哪些位做什么。例如:明确表示了 $A_9 \sim A_0$ 是在找行号, $A_{11} \sim A_{10}$ 是在产生片选逻辑然后找芯片,每一组上面的芯片存 $D_7 \sim D_4$, 下面的芯片存 $ D_3 \sim D_0 $。

另一道例题:

某半导体存储器,按字节编址。其中,0400H~07FFH为ROM区,选用EPROM芯片(1KB/片);0800H~13FFH为RAM区,选用RAM芯片(2KB/片和1KB/片)。地址总线A15~A0(低)。问:给出地址分配和片选逻辑,并画出M框图。

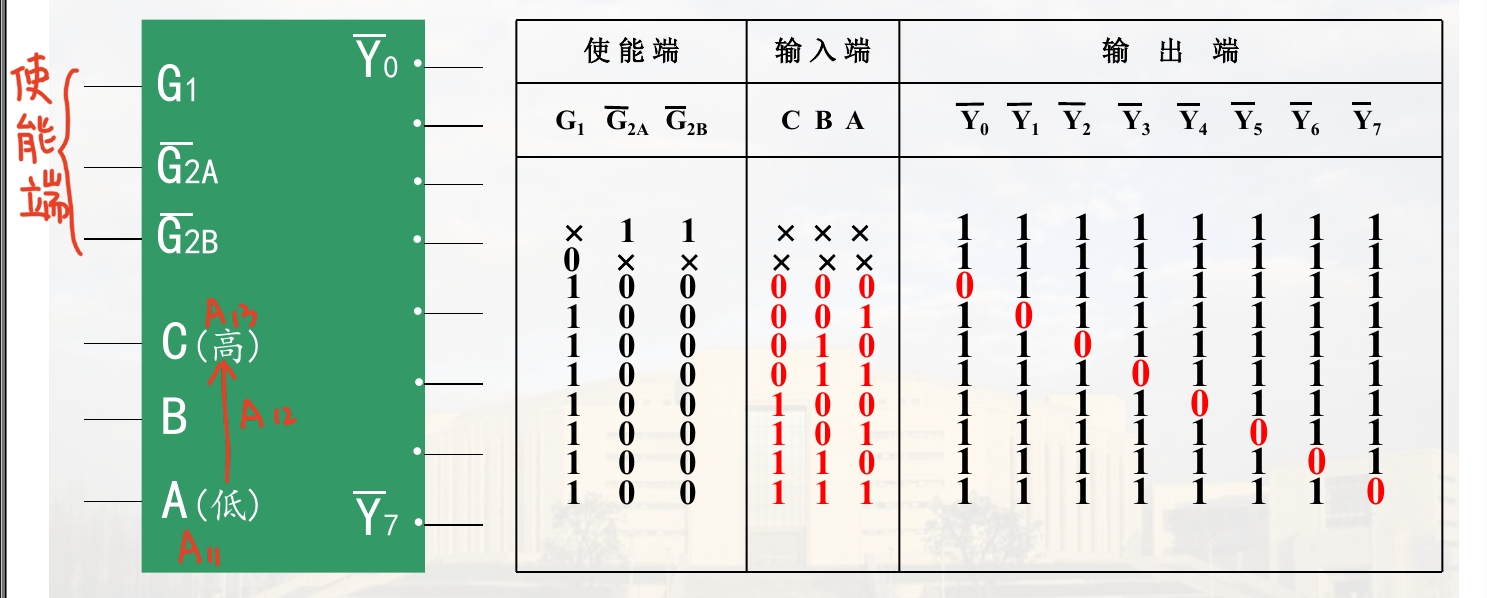

在上面的题目中,出现了 $ \overline{A_{12}}A_{11}A_{10} $ 和$ A_{12} \overline{A_{11}} ~\overline{A_{10}} $,这个时候如果每一个片选信号都单独画就很麻烦。所以引入译码器。

译码器的使用

3 - 8 译码器(74LS138译码器)

三个使能端,要求一个输入始终为 1 ,另两个输入为 0 的时候才启用这个译码器。

A B C 就是输入端,根据输入的选择唯一的有效输出。

2 - 4 译码器

和上面基本一样,但是只有一个使能端,两个输入端,四个输出端。

两个 2 - 4 译码器可以组成一个 3 - 8。拿最高位作为两个使能端的输入:如果为 1 那么就走译码器 A,如果 0 就走译码器 B,A 输出 7 ~ 4, B 输出 3 ~ 0。

地址译码方式

全地址

使用全部地址总线信号。所有高位的地址信号都作为输入、使能信号。使得存储器每一个空间具有唯一的地址。

部分地址

仅仅使用一部分地址信号作为输入使能信号。其他的部分悬空。会使地址出现重叠区。

例如:0000 和 1000 可能选中同一片,如果最高位没被检测

DRAM 的刷新

刷新与重写的区别

- 刷新:非破坏性读出的 DRAM,需要补充电荷保持原来的信息。

- 重写(再生):破坏性读出后重写,恢复原来的信息。(只针对单管组成的 DRAM)

最大刷新间隔:2 ms(此时间内必须对所有的单元都刷新一遍)

刷新方法:按行读。

刷新一行要用的时间即为刷新周期(存取周期),刷新周期数有行数决定。($T = \frac{2 ms}{lines}$)

对主存的访问:CPU 访存 & 动态芯片的刷新(刷新地址计数器提供行地址,定时刷新)

刷新周期的安排方式

-

集中刷新:2 ms 内选取一部分时间专门拿来刷新,这部分时间不允许 CPU 访问。

实时性不高的时候可以用

-

分散刷新:读写和刷新间隔安排

低速系统内常用

-

异步刷新:个刷新周期分散在 2 ms 内,隔一段时间(每一个刷新周期)刷新一行。

刷新请求是 DMA 请求,属于 DMA 控制的特殊情况。

主存的校验

校验方式:采用冗余校验思想。

校验码:将待写的有效代码和增加的校验为一起,按照约定的校验规律进行编码

码字:若干为代码组成一个字

码距:一种码制中,任何两个码字间的举例可能不同。将各合法码字间的最小举例称为这种码字的码距。

主存中采用奇偶校验:

添加一位校验码,使得所有的 1 的个数为 偶数/奇数 即为 偶/奇 校验。

奇偶校验的码距为 2.

Chapter 5 - 输入输出设备

I / O 系统包含硬件部分和软件部分。硬件部分就是 I / O 设备、接口和系统总线。软件部分包含:

- 设备控制程序(设备自带):固话在 I / O 控制器中的控制程序(如控制外设的 R、W,总线上访问控制信息)

- 设备驱动程序:OS 中针对各种外设的设备和驱动程序。

- 用户 I / O 程序:如中断服务程序、DMA

连接方式见该复习资料上篇。

总线

一组能为多个部件分时共享的信息传送线路,以及相应的控制逻辑。

分时:发送部件通过 OC 组件或三态门分时发送信息。

共享:由打入脉冲将信息送入指定接受部件

实体:一组传送线与相应控制逻辑

按照功能分类:

- CPU 内总线 (ALU 总线 ) DB(或多种总线类型)

- 部件内总线 (局部总线、片级总线),AB,CB,DB

- 系统总线(板级总线),AB,DB,CB

- 外总线(通信总线),DB(复用AB),CB

按照时序控制方式划分:

- 同步总线:由统一时序(时钟周期、同步周期)控制总线实现传送操作。

- 异步总线:无固定时钟周期划分,总线周期时间由传送实际需要决定,用异步应答控制总线传送操作。

- 扩展同步总线:以时钟周期为时序基础,允许总线周期中的时钟数可变。

区分:

- 时钟周期(节拍): CPU 一步(一次内部数据通路传送)操作的时间

- 总线周期:经过总线的一次数据传送(访存)时间,包含

- 工作周期:指令周期的一个操作阶段,可包含多个总线周期

按照数据传送格式划分:

- 并行:通过一组总线同时传送信息

- 串行:通过一条总线分时逐位传送

接口

(硬件)接口指主机和外设的交接部分,位于系统总线和外设之间。

为了完成通信,接口内部必须包含三类不同功能的寄存器(也称为端口):

- 数据端口 (Data Port)

- 位置: 图中最上方。

- 功能: 存放实际要传输的数据(例如:从键盘敲入的字符,或者要发送给打印机的文档数据)。

- 流向: 双向(CPU $\leftrightarrow$ 外设)。图中标注了 DB(Data Bus,数据总线),说明数据是通过数据总线在 CPU 和接口之间传输的。

- 状态端口 (Status Port)

- 位置: 图中中间。

- 功能: 存放外设当前的工作状态(例如:打印机是“忙”还是“闲”?是否有“缺纸”错误?)。

- 流向: 外设 $\rightarrow$ CPU。注意箭头方向,状态信号由外设产生,存入接口,最终被 CPU 读取(图中细线指向了上面的 DB,意味着状态信息也是通过数据总线读回 CPU 的)。

- 控制端口 (Control Port)

- 位置: 图中最下方(有一个红色激光笔亮点)。

- 功能: 存放 CPU 发出的控制命令(例如:启动设备、停止设备、复位)。

- 流向: CPU $\rightarrow$ 外设。CPU 发出指令,经由接口传达给外设。

功能:

- 寻址:接受地址码,选择接口中的寄存器(端口)供 CPU 访问。

- 数据缓冲:实现主机与外设的速度匹配。缓冲深度和传送的数据量相关。

- 预处理:串并格式转换(对串口),数据通路宽度转换(并口),电平转换

- 控制功能:传送控制命令与状态信息,实现 I / O 传送控制方式

分类

按数据传送格式划分:

- 并行:两头都是并行。适用于设备本身并行,离主机近的情况。

- 串行:接口与总线并行,接口与外设串行,数据逐位分时传送,适用于本身串行,离主机远,或需要减少传送线的情况

按时序控制划分:

- 同步接口:接口和系统总线的信息传送由统一时序信号控制

- 异步接口:异步应答传送信息。

按 I / O 传送控制方式划分:

- DMA 接口

- 中断接口

- 直接程序传送接口

模型机系统总线

共 78 条, 16 条电源线和地线,16条地址线,16条数据线,30条控制信号线(R / $\overline{W}$)

- 电源线 10 条 +5V x2, -5V x2, +12V x 2, -12V x 2, 备用电源线 2 条

- 地线 4 条

- 附加地 2 条 :分开电源和信号线,利于抑制干扰

- 地址线 16 条,寻址空间 64 KB 包含 I / O 端口地址(统一编址模式)

- 数据线 16 条

- 控制信号线 30 条

- reset(复位信号线):1条

- 同步定时信号线:6 条

- 异步应答信号线:3 条

- 总线控制权信号线:3 条。BREQ(请求),BACK(应答),BUSY(繁忙)

- 中断请求与批准信号线:10 条。IREQ 0 ~ 7(8 种设备中断),INTA(相应中断请求),INT(中断请求)

- 优先权判定线:2 条

- 数据传送控制信号: 5 条。 MEMR,MEMW,IOR,IOW,BHEN(判断总线是否可用)

直接程序续传送方式与接口

用 I / O 指令编程实现信息传送

外设状态:在接口中设置状态字表示这些状态。

空闲(00),工作(01),结束(10)(代表完成一次工作)

查询流程:

flowchart TD

%% 样式定义

classDef box fill:#4a86e8,stroke:#000,stroke-width:2px,color:white;

classDef diamond fill:#4a86e8,stroke:#000,stroke-width:2px,color:white,shape:rhombus;

classDef textLabel fill:none,stroke:none,color:#e06666,font-size:14px;

%% 流程节点

Start( ) --> Step1[启动外设]:::box

Step1 --> LoopPoint( )

LoopPoint --> Decision{外设工作完成?}:::diamond

%% 循环逻辑

Decision -- N --> LoopPoint

%% 成功逻辑

Decision -- Y --> Action[输入/出操作]:::box

Action --> End( )

%% 侧边文字标注 (使用不可见节点辅助定位)

NoteText[判断状态字]:::textLabel

Step1 ~~~ NoteText ~~~ Decision

优缺点:硬件开销小;实时处理能力差,并行程度低。

应用场合:对CPU效率要求不高的场合,或诊断、调试过程

5 - 4 中断

概念

CPU 暂时停止执行现行程序,转去执行某个随机事态服务的中断处理程序。处理完毕后自动恢复原程序的执行。

实质:程序切换

-

方法:保存硬现场(PSW)断点(PC )和软现场(其他寄存器)、获取服务程度入口地址;返回断点

-

时间:一条指令完整结束时切换,保证程序的完整性。

-

特点:随机性

中断和转子(调用子程序 )的相同与不同:

- 相同:都要保护断点现场。都要获取入口地址传入 CPU、PC

- 不同:转子是有意安排,中断是随机获取;转子的调用有段内和段间,中断的调用只有段间。转子调用的程序和她自己关系很大(主从关系),中断则几乎无关。

注:转移(GOTO)跳了就不回来了。

中断的分类:

- 硬件中断(由硬件请求信号引发)和软中断(INT 指令引发中断)

- 内中断(中断源来自主机内部)和外中断(中断源来自主机外部)

- 可屏蔽中断(可通过屏蔽字屏蔽这类请求,关中断的时候不响应)和非屏蔽中断(请求与屏蔽字无关,请求的相应和开关中断无关),只有外部可屏蔽中断有 IT 周期

- 向量中断(硬件提供服务程序入口地址)和非向量中断(软件提供服务程序入口地址)

中断的应用:

- 管理中低速 I/O 操作

- 处理故障

- 实时处理

- 人机对话

- 多机通信

中断系统

由硬件部分,软件部分组成。硬件部分是 I/O 接口和中断请求源(外设里面)。软件部分是中断服务程序和中断向量表(实际是内存中的一维表,存放中断服务程序的入口地址)

中断请求源

外部硬件中断源: 8 种。 IREQ 0 ~ 7

内部请求源:系统时钟、实时时钟、通信中断、显示器、打印机、键盘、软盘、硬盘、掉电、溢出、校验错中断……依次从 0 开始编号。

软中断:模型机软中断是 INT 11~ n

中断服务程序

由系统提供。在主存中的空间不必连续。

中断向量表

存放在模型机中主存的二号单元开始。向量地址 = 中断号 + 2

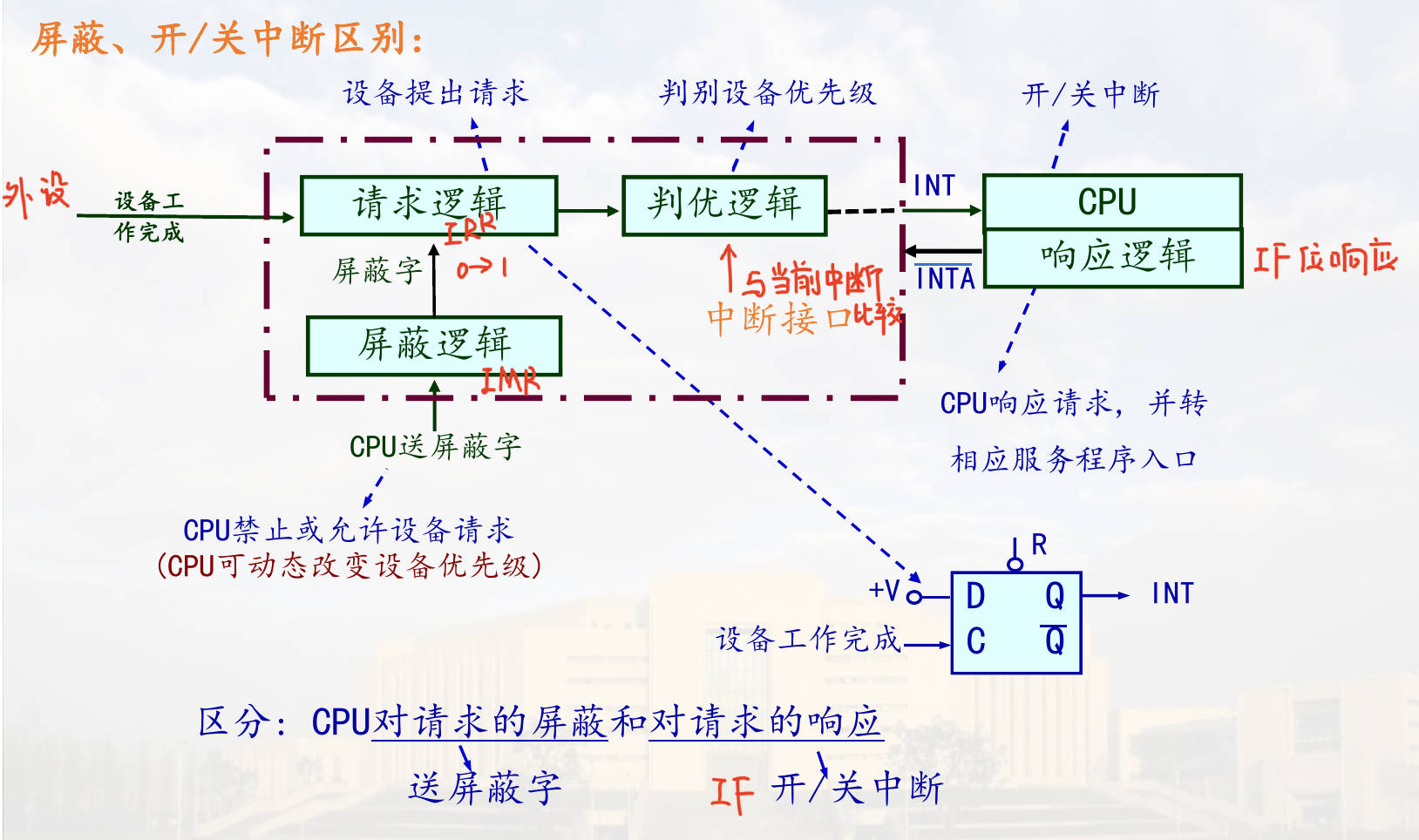

中断请求方式(外部可屏蔽中断

这张图片展示了产生到响应的完整过程

中断请求产生

有两个要求:

- 外设工作完成:接口中的状态字寄存器被设置成 1 。代表外设干完了一次/准备好工作了。

- CPU 允许该外设请求:在这个接口的控制寄存器中,屏蔽字不为 1.

满足这两个要求之后,就可以发出有效请求了。

两个发出有效请求的方式:

-

上述两个要求先求与,在发送给请求触发器,请求触发器直接发送有效请求(分散屏蔽)

-

完成条件直接发送给请求触发器,然后发出的请求和屏蔽求与,生成有效请求。(集中屏蔽)

比较维度 左图:先屏蔽后请求 右图:先请求后屏蔽 (IMR) 逻辑顺序 屏蔽信号 $\rightarrow$ 触发器 触发器 $\rightarrow$ 屏蔽门电路 屏蔽时的表现 触发器不翻转,无反应 触发器翻转置1,信号被拦截 屏蔽解除后 刚才的请求已消失,无法响应 刚才的请求立刻通过,可以响应 别名 分散屏蔽 集中屏蔽 (IMR) 现代应用 极少见,仅用于极简单的嵌入式 标准做法 (x86, ARM等均采用)

中断请求传送

在不同的总线架构中,采用不同的传送方式。

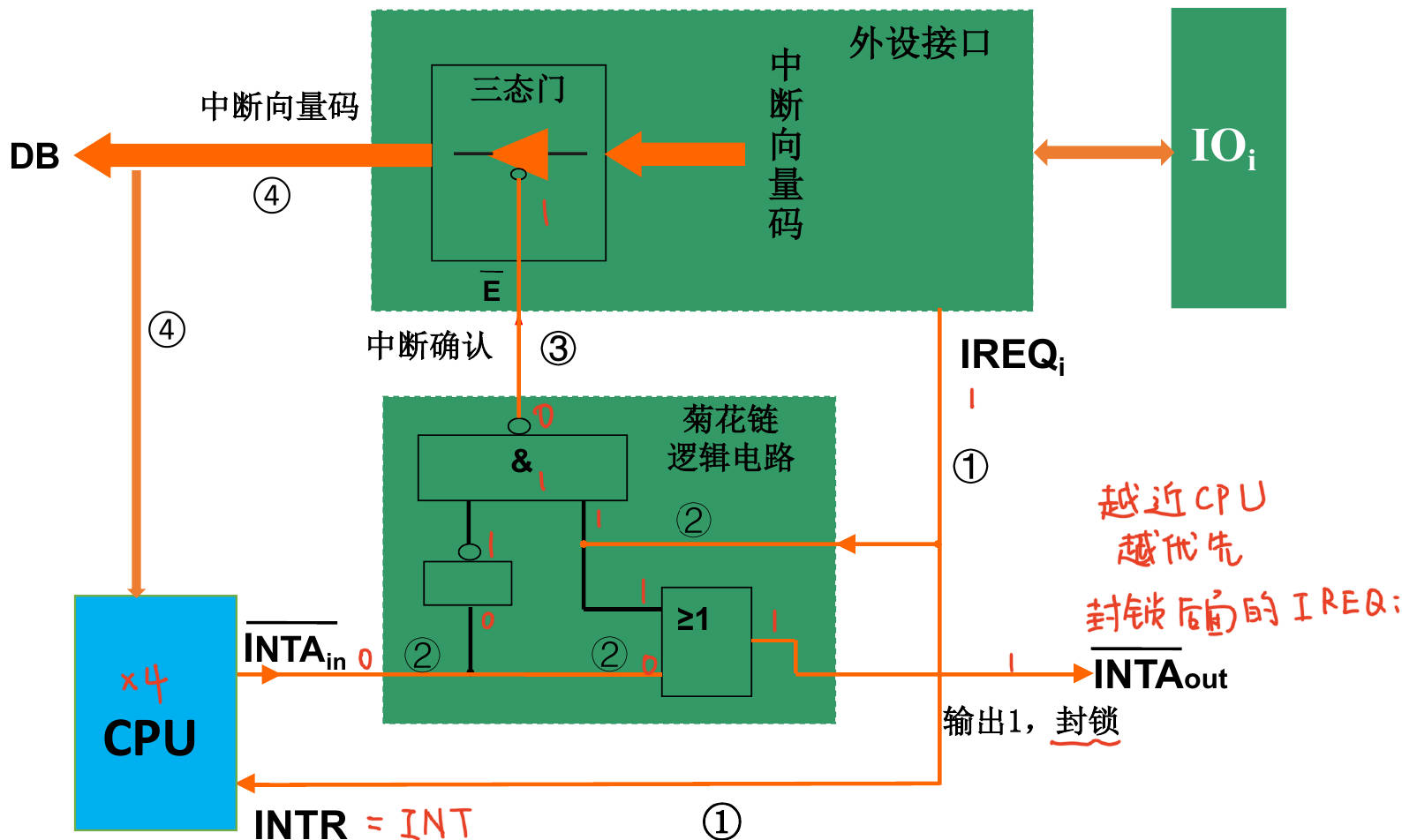

当是辐射型架构的时候,采用单独请求线。响应速度快,但是引脚线固定,不易拓展。

当是总线型架构的时候,采用公共请求线。易拓展,但是分不出谁是谁。因此衍生:二维结构和独立公共并存的方式(区分优先级)

中断请求判优与屏蔽

CPU 一时只能干一件事,所以同一时间需要判断先做哪一个。涉及到中断判优处理逻辑电路。

中断判优顺序:故障中断 > DMA > 外中断输入 > 外中断输出。

现行程序和中断请求间判优:

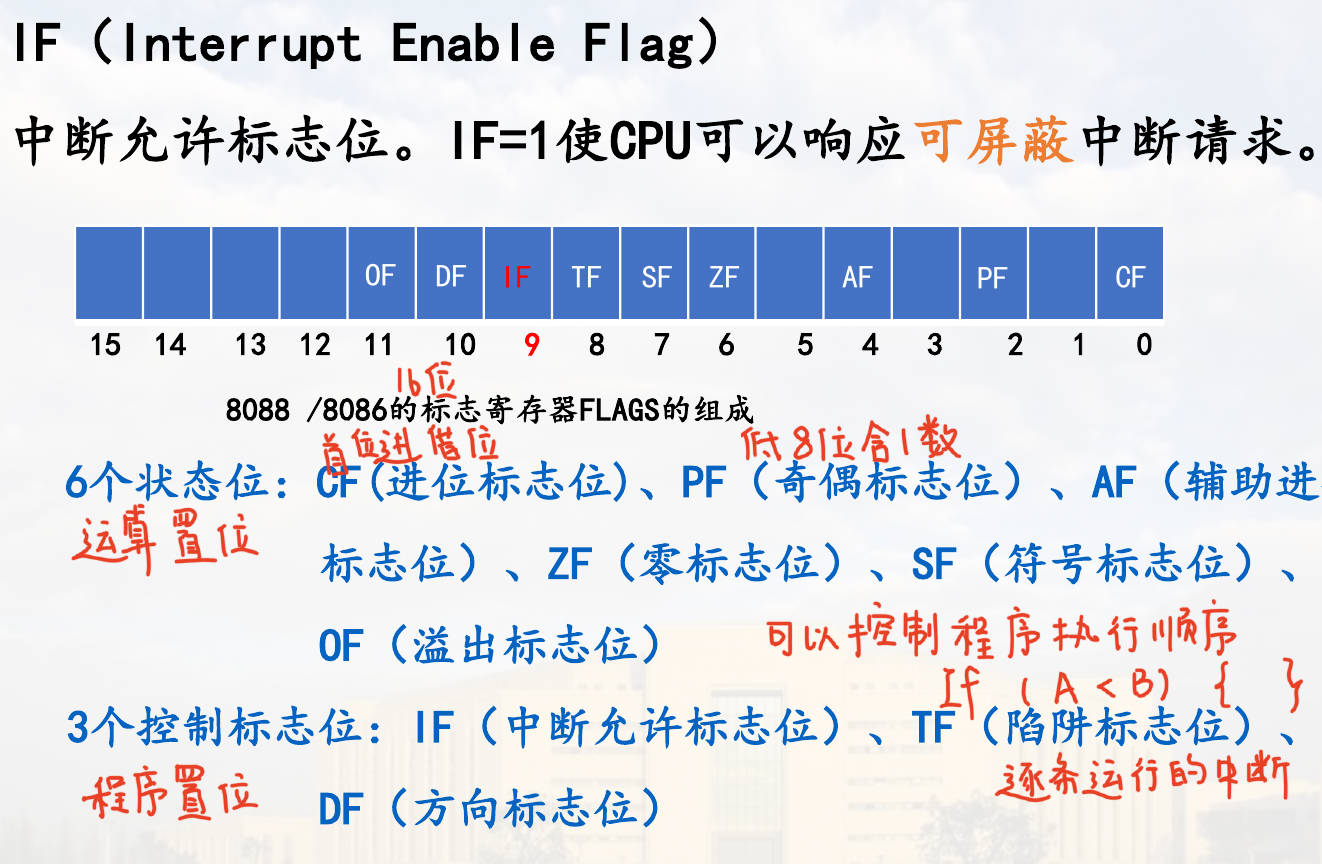

1、简单判优:利用 PSW中的 IF 控制位, 为 0 为关中断,不响应中断,为一为开中断,响应中断。

2、在 PSW 中设置程序优先级别

3、外设请求的判优:软件(运行程序查询顺序确定优先级)、硬件(并行优先排队逻辑、链式优先排队逻辑、二维结构的优先排队、中断控制器判优等。)

中断服务程序入口地址获取

分为向量中断(硬件方式)和非向量中断(软件编程方式)

向量中断方式

-

中断向量:采用向量化的中断响应方式,将中断服务程序的入口地址(PC)及其程序状态字(PSW)存放在特定的存储区(中断向量表)中,所有的中断服务程序入口地址和状态字一起,称为中断向量。

-

中断向量表:即用来存放中断向量的一张表。在实际的系统中,常将所有中断服务程序的入口地址(或包括服务程序状态字)组织成一张一维表格,并存放于主存的一段连续的存储区(一般在主存首部),此表就是中断向量表。

在模型机中,这张表占用 0 ~ 1023 地址单元。每个中断源占 4 个单元,共 256 个中断源。

分为专用区(0~4),系统保留区(5~31),用户扩展区(32~255)

-

向量地址:访问中断向量表的地址码,即读取中断向量所需的地址(也可称为中断指针,入口地址的地址)。

-

向量中断:将各个中断服务程序的入口地址(或包括状态字)组织成中断向量表;响应中断时,由硬件直接产生对应于中断源的向量地址;据此访问中断向量表,从中读取服务程序入口地址,由此转向服务程序的执行。这些工作在中断周期IT中由硬件直接实现(不需编写程序实现)。

-

地址获取方式:向量地址 = 中断类型码(硬件中断) / 中断号(软中断) * 4(每个中断源占的字节数)。高 2 B 是段基地址(CS 段的首地址),低 2 B 是段内偏移地址

非向量中断

CPU响应中断时只产生一个固定的地址,由此读取中断查询程序的入口地址,从而转向查询程序,通过软查询,确定被优先批准的中断源,然后分支进入相应的中服务程序。(可以改变中断服务的优先级)

响应中断

响应中断的条件

1)有中断请求信号发生,如IREQi或INT n。

2)该中断请求未被屏蔽。

3)CPU处于开中断状态,即中断允许触发器 TIEN=1(或中断允许标志位IF=1)。

4)没有更重要的事件要处理(如因故障引起的内部中断,或是其优先权高于程序中断的DMA请求等)。

5)CPU刚刚执行的指令不是停机指令(HLT指令)。

6)在一条指令完整结束时响应(因为程序中断的过程是程序切换过程, 不能在一条指令执行的中间就切换)。

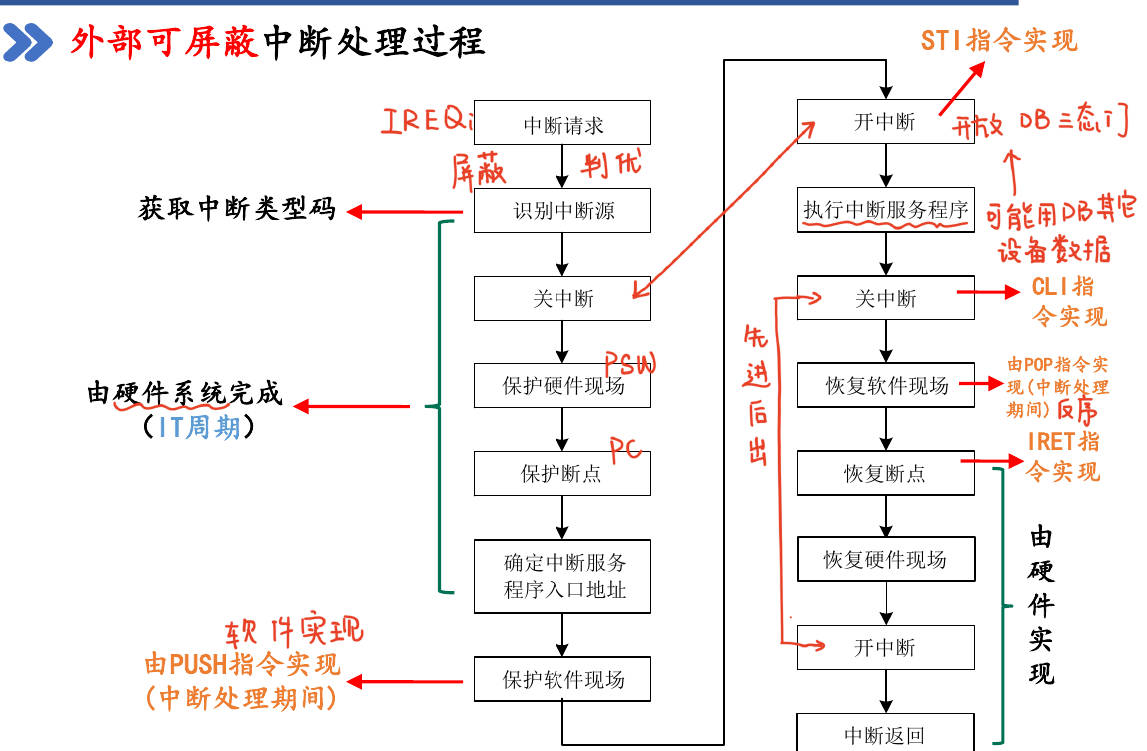

响应中断的过程

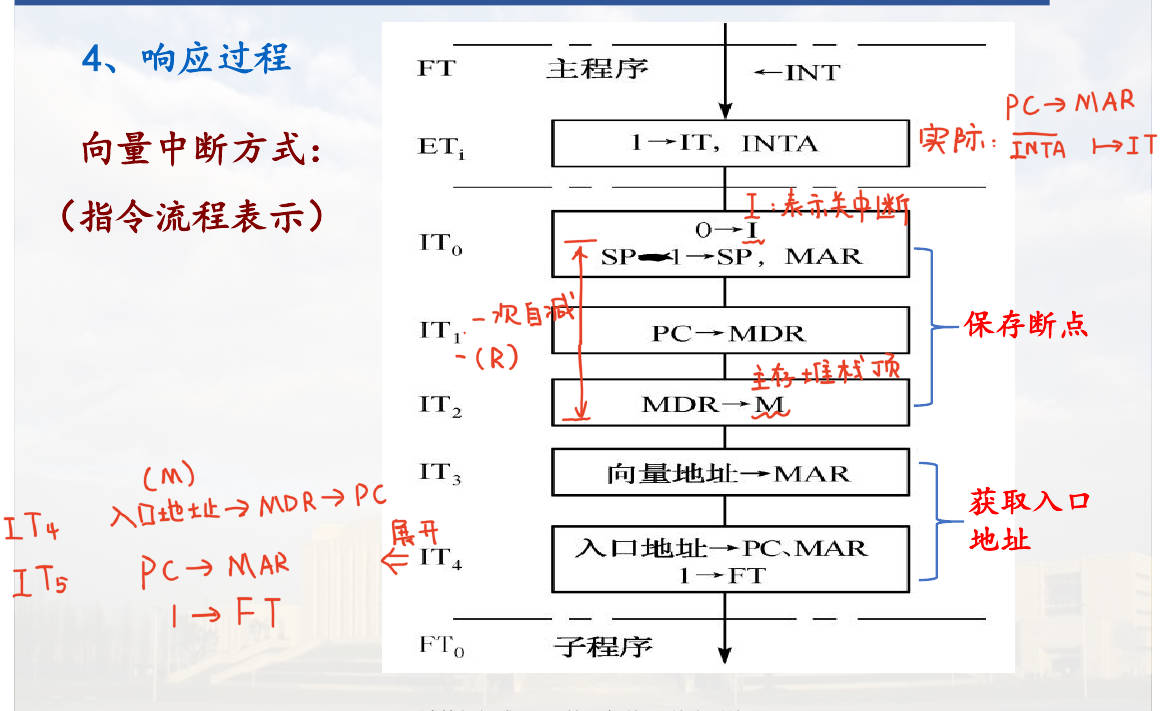

向量中断方式:发送响应信号 INTA(低电平有效),进入中断周期(IT),关中断保存断点,获得中断号,转换为向量地址,查向量表,取中断向量,转中断服务程序。这整个过程都是硬件完成的(CPU 执行中断隐指令)

关中断:防止 DB 中其他数据压入堆栈,针对压栈、弹栈时期

流程:

阶段 0:中断判优与确认 ($ET_i$)

- 流程: $1 \to IT, INTA$

- 逻辑: 当外部设备发来中断信号(INT),且CPU允许中断(PSW中I=1),CPU在指令执行结束周期(ET)发出中断响应信号(INTA, Interrupt Acknowledge)。

- 笔记细节: 你标注了

PC -> MAR和实际: /INTA -> IT。这意味着在响应阶段,硬件其实已经开始准备总线交互了。阶段 1:关中断与保护现场 ($IT_0 \sim IT_2$)

这是最关键的“原子操作”。

- $IT_0$: 关中断与栈准备

0 -> I: 为什么要这一步? 这是为了防止“中断嵌套”导致混乱。在保存当前断点(PC)的过程中,绝不能再被新的中断打断,否则原来的PC值可能会丢失。SP - 1 -> SP, MAR: 堆栈通常是向下生长的(地址从高到低)。先将栈指针减1,然后把新的栈顶地址送入MAR,准备写入数据。- $IT_1$: 传送断点

PC -> MDR: 把当前的PC值(即断点,下一条本该执行的指令地址)送到数据缓冲寄存器。注意:此时PC还没变,仍是主程序的断点。- $IT_2$: 压栈(保存断点)

MDR -> M: 这是一个写内存操作。将MDR里的PC值,写入到MAR指向的内存地址(栈顶)。- 逻辑总结: 到这里,主程序的回程票(断点)已经安全地保存在内存堆栈里了。

阶段 2:获取中断服务程序入口 ($IT_3 \sim IT_4$)

这里是向量中断的核心逻辑。这也是你手写笔记修正最多的地方。

- $IT_3$: 向量地址送地址总线

向量地址 -> MAR: 这里的“向量地址”不是中断服务程序的真实入口地址,而是一个指针。它是由硬件(中断控制器)产生的,比如打印机中断产生0x0010,键盘产生0x0020。- 逻辑: CPU拿着这个硬件给的号(向量地址),去内存里查“中断向量表”。

- $IT_4$ (及手写补充): 取入口地址并跳转

- 原图写的是:

入口地址 -> PC, MAR。- 你的手写补充(非常重要且准确):

IT4: (M) -> MDR -> PC(从内存读出数据到MDR,再给PC)。IT5: PC -> MAR,1 -> FT。- 深度解析: 这是一个间接寻址的过程。

- 硬件给出向量地址(指向内存某处)。

- CPU读取该内存地址中的内容(这才是真正的服务程序入口地址)。

- 将这个内容塞入 PC。

- 一旦PC变了,下一条指令取指($FT$)时,CPU就会自动跳到中断服务程序去执行了。

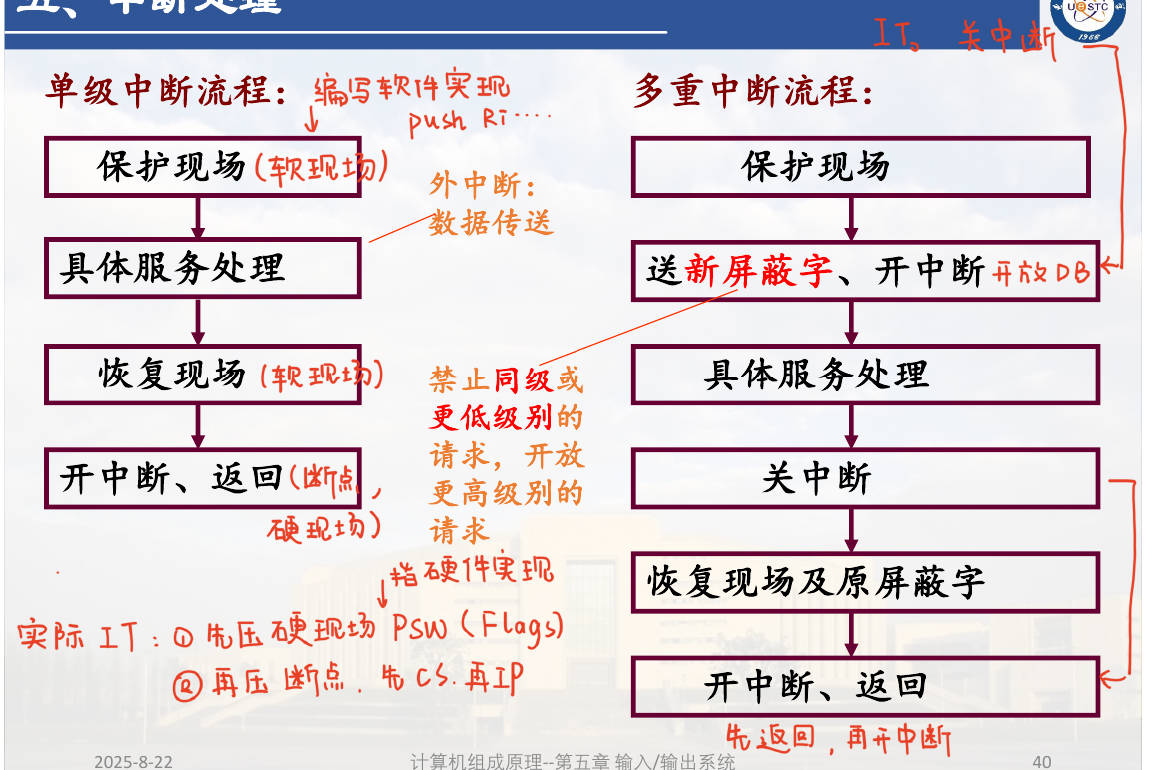

中断处理

- 单级中断:CPU响应后只处理一个中断源的请求,处理完毕后才能响应新的请求。

- 多重中断:在某次中断服务过程中,允许响应处理更高级别的中断请求。

中断流程:

允许多重中断的处理方式:不断堆栈进行中断嵌套。

恢复现场与返回原程序 在编制中断服务程序时应遵循一个原则:在响应过程、保护现场、恢复现场等过渡状态中,应当关中断,使之不受打扰。

总结

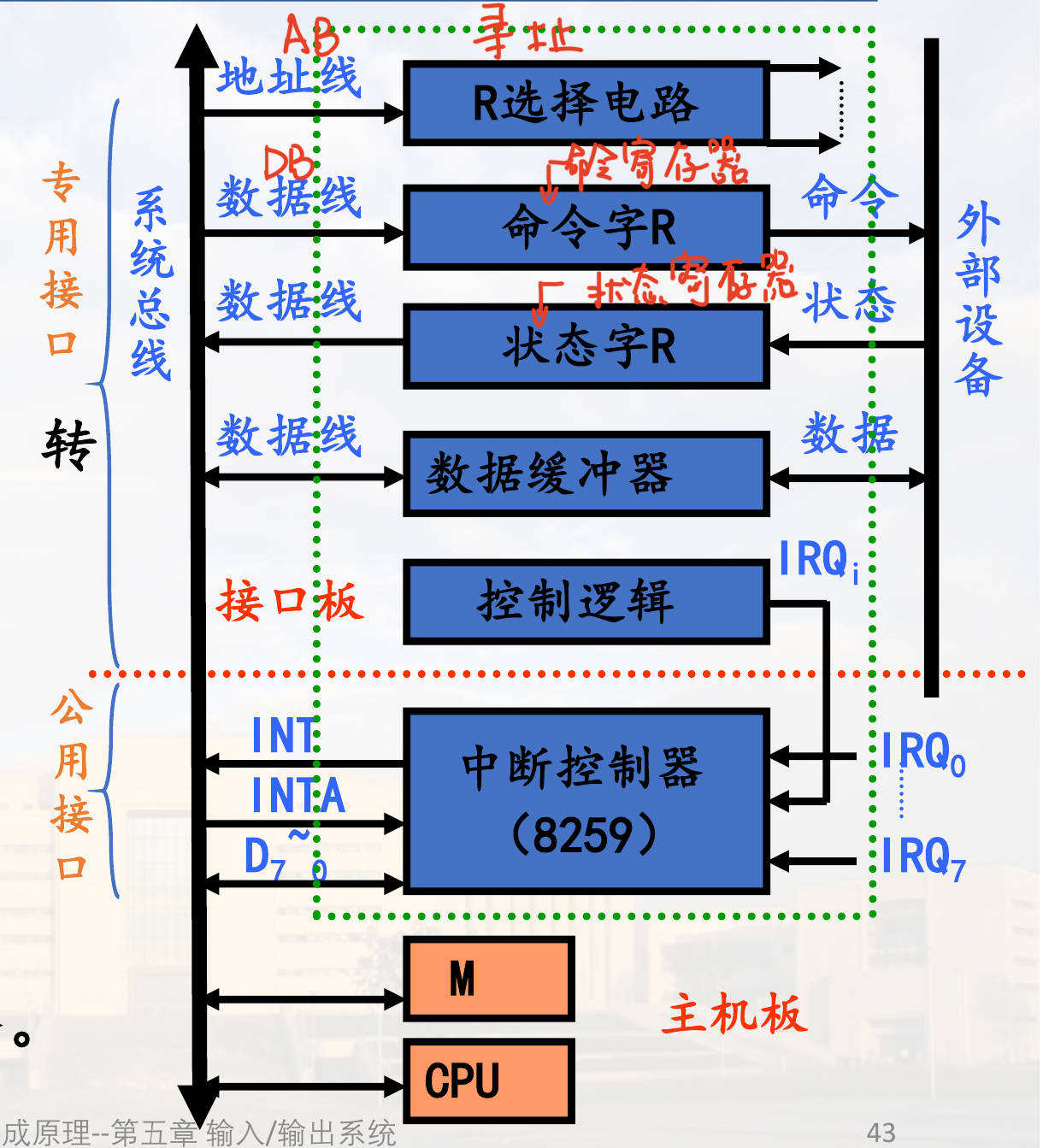

中断接口

组成

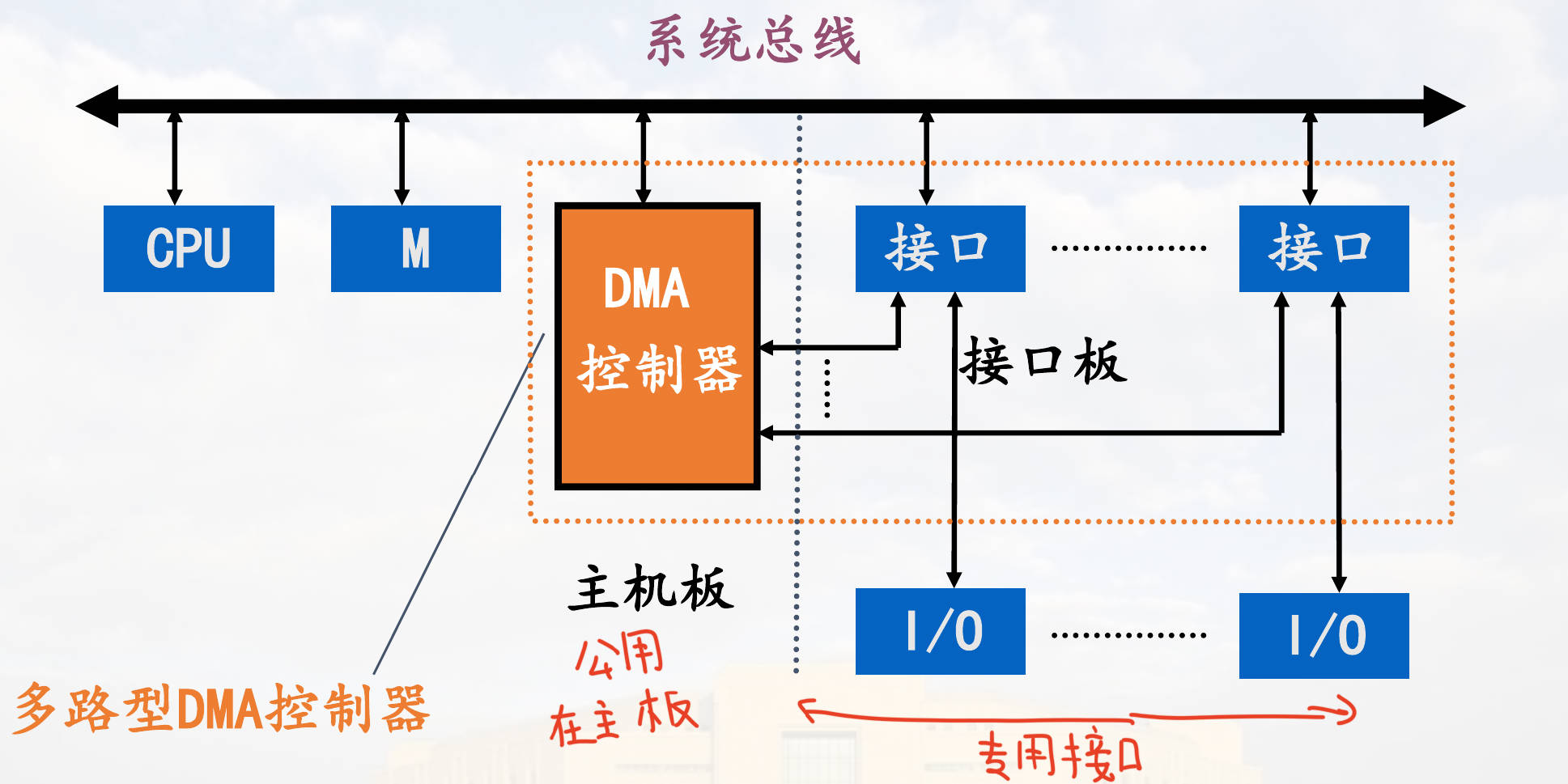

其中,专用接口位于外设内,公用接口位于主板上。

寄存器选择电路:对接口寄存器寻址

命令字寄存器:接受 CPU 向外设发送的命令字(位数和含义代表不同命令),转换为相关操作命令发送给外设。

状态字寄存器:代表接口和设备的运行状态

数据缓冲器:用于缓冲数据

控制逻辑:产生请求信号、电平转换逻辑、串并转换逻辑、针对设备特性的逻辑

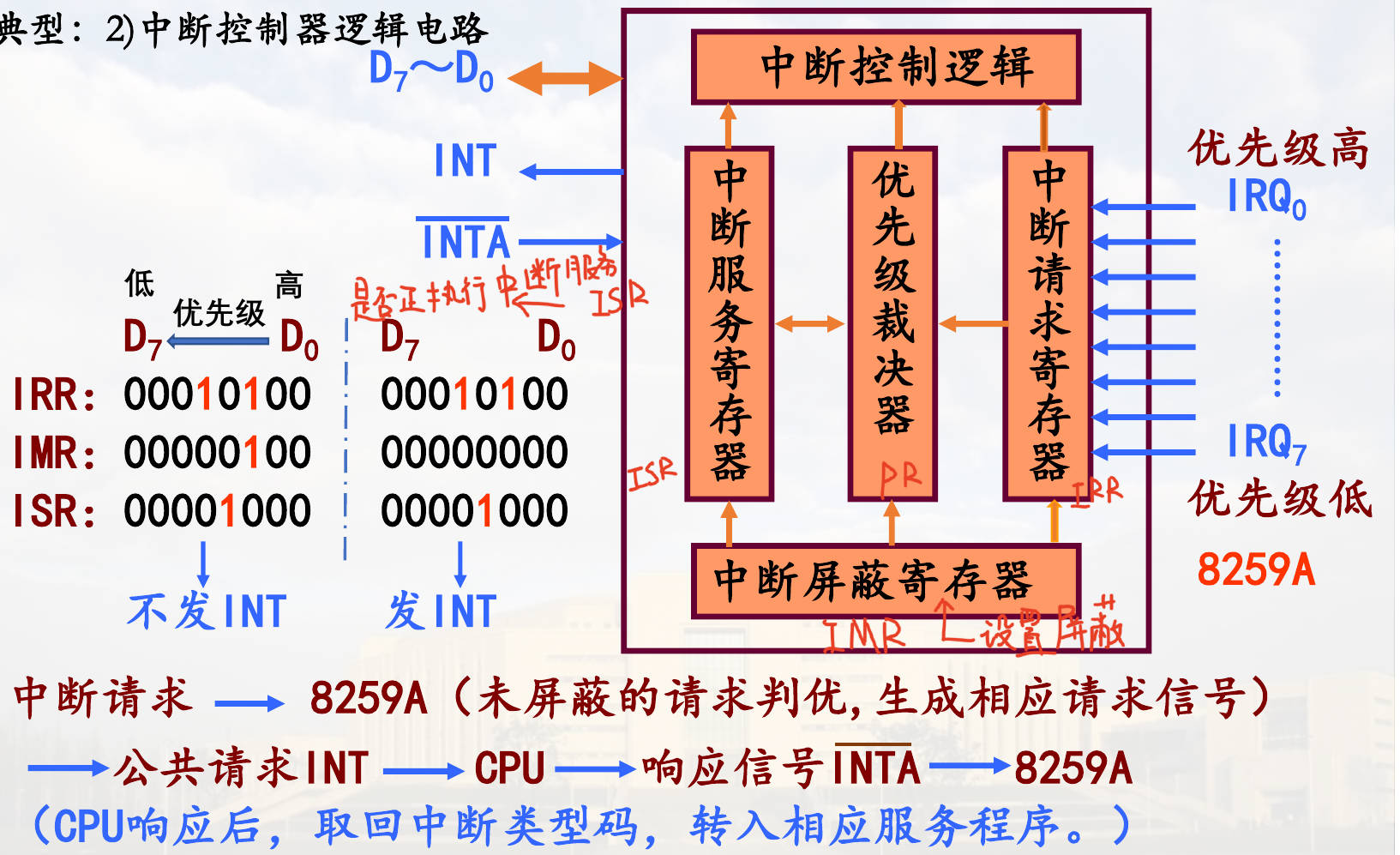

公用中断控制器:接受外设中断请求、判优、送出公共中断请求。接受中断,送出中断控制码/号

工作过程

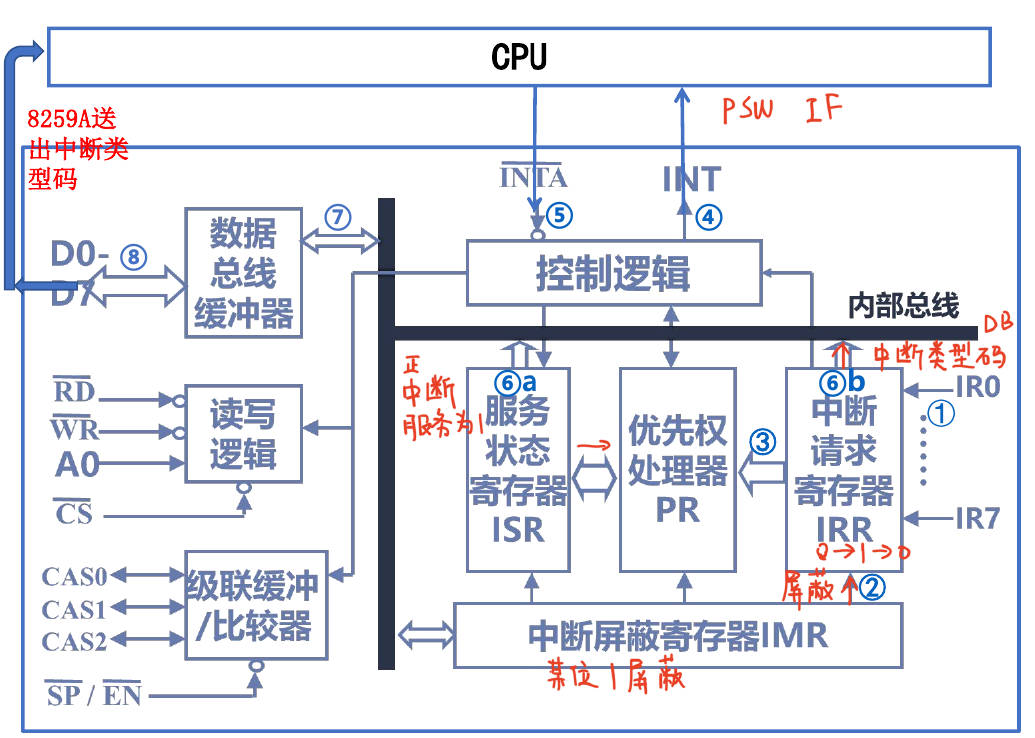

1、初始化:设置工作方式,送屏蔽字、送中断号(确定高位)

注:确定高位指 8 位的中断号,初始化的时候把最高的五位预先填进去。因为那玩意就 8 个针脚,只能处理三位

2、发送启动命令(送命令字),启动设备。

3、设备完成工作,发送中断请求

4、中断控制器汇集各中断请求,进行屏蔽判优,然后形成中断号,向 CPU 发送 INT 请求

(4.5、 CPU 返回 INTA 响应)

5、中断控制器送出中断号

6、CPU 执行中断隐指令操作,进入服务程序

1. 初始化 (Initialization)

- 动作: 操作系统启动时,或者驱动程序加载时,CPU 通过数据总线向 8259 (中断控制器) 写入初始化命令(ICW)。

- 核心逻辑:

- 设置工作方式: 告诉 8259 是电平触发还是边沿触发?是单片还是级联?

- 送屏蔽字 (Masking): 告诉 8259 哪些中断先闭嘴(Mask=1),哪些可以放行。

- 送中断号 (确定高位): 这就是我们刚才讨论的,告诉 8259:“你的基址是

0x20”,确立中断向量的高 5 位。2. 发启动命令 (Start Command)

- 动作: CPU 执行

OUT指令,向接口板的 命令字寄存器 写入数据。- 核心逻辑: 这相当于按下“启动开关”。接口收到命令后,控制逻辑会驱动外部设备开始工作(比如打印机开始走纸,网卡开始监听)。此时,CPU 任务暂时完成,可以转头去处理别的进程。

第二阶段:物理世界的运作 (硬件独立运行)

3. 设备完成工作,申请中断

- 动作: 外设干完活了(或者出错了/收到数据了)。

- 核心逻辑:

- 设备状态改变,接口板上的 状态字寄存器 更新(比如

Ready位置 1)。- 控制逻辑 检测到这个状态变化,且发现“中断允许”是开着的,于是拉高 IRQ 线(比如

IRQ7)。- 这个电信号顺着电路板传到了 8259 的引脚上。

第三阶段:谈判与握手 (关键的硬件交互)

这是最精彩的“三人舞”环节(外设、8259、CPU)。

4. 8259 的内部裁决

- 动作: 8259 收到 IRQ 信号。

- 核心逻辑: 它必须在一瞬间完成三个判断:

- 屏蔽 (Mask): 这个 IRQ 被屏蔽了吗?(如果 IMR 寄存器里对应位是 1,直接忽略)。

- 请求 (Request): 记录下来,置位 IRR (Interrupt Request Register)。

- 判优 (Priority): 此时有没有更高级的中断正在处理?(比较 ISR 寄存器)。

- 结果: 如果一切通过,8259 向 CPU 发出 INT (High Level) 信号。

[缺失的步骤 5]:CPU 的响应 (INTA)

- 注意: PPT 文字直接跳到了 6,但图中画了

INTA线。- 逻辑: CPU 在执行完当前指令后,检测到

INT引脚有信号。如果 CPU 内部的中断允许标志 (IF) 是开的,CPU 就会回送一个信号 —— INTA (Interrupt Acknowledge)。- 含义: CPU 说:“我听到你了,准备处理。你是谁?”

6. 送出中断号 (Vector Transmission)

- 动作: 8259 收到 CPU 的

INTA信号。- 核心逻辑: 8259 知道 CPU 准备好了,于是把刚才拼凑好的 8位中断号(高5位基址 + 低3位引脚号)放到数据总线 ($D_7 \sim D_0$) 上。

第四阶段:移交控制权 (软硬交接)

7. 执行中断隐指令,进入服务程序

- 动作: CPU 从数据总线上拿到中断号。

- 核心逻辑 (由硬件自动完成,无需写代码):

- 关中断: 防止干扰。

- 保护断点: 把当前的 PC 和 PSW 压入堆栈(Stack)。

- 查表跳转: 拿着中断号去内存里的“中断向量表”查找入口地址,把 PC 指针指向那个地址。

- 结果: 下一个时钟周期,CPU 开始执行中断服务程序 (ISR) 的第一行代码。

DMA 方式

DMA,即直接存储器访问(Direct Memory Access),它指这样一种传送控制方式:依靠硬件直接在主存与外围设备之间进行简单、批量、快速的数据传送,在传送过程中不需要CPU的干预。

实质:程序暂停(在一条指令完整结束之后,主程序暂停(MAR MDR IR 控制逻辑和总线的三态门全部关闭)),同样具有随机性。

应用:DMA传送方式一般应用于主存与高速I/O设备之间的简单数据传送。高速I/O设备包括磁盘、磁带、光盘等外存储器,以及其它带有局部存储器的外围设备、通信设备等等。如 DRAM 的异步刷新,磁盘读写。

DMA传送是直接依靠硬件实现的,可用于快速的数据直传,传送过程无需CPU参与。也正是由于这点,DMA方式不能处理复杂事态。因此,在某些复杂场合常将DMA与程序中断方式相结合,二者互为补充。典型的例子是磁盘调用,磁盘读写采用DMA方式进行数据传送,而对寻道正确性的判别、批量传送结束后的处理,则采用中断方式。

DMA 控制器和接口的连接

允许各设备以字节为单位交叉传送,或以数据块为单位成组传送。

DMA 控制器的功能

初始化阶段:接收初始化信息 (传送方向、主存首址、交换量)

传送前:接收外设DMA请求,判优,向CPU申请总线

传送时:接管总线权,发地址、读/写命令

接口功能

初始化时:接收初始化信息(外设寻址信息)。

传送前:向DMA控制器发请求

传送时:传送数据